# I/O and exceptions

# $\mathbf{O}$

# ???

Besides the cache/memory management unit, what sorts of things does the processor need to talk to?

## Abstraction of I/O

$\odot$

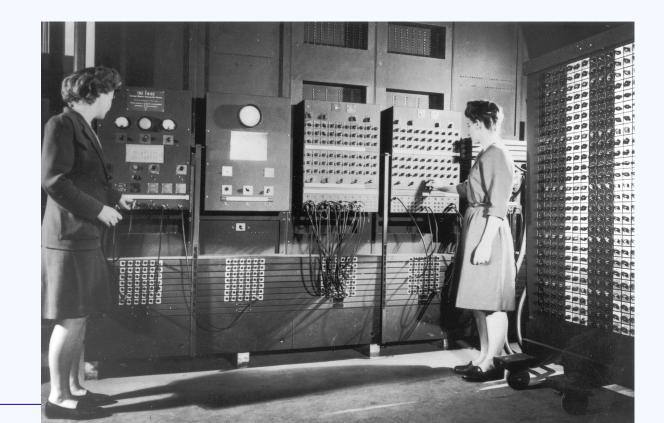

### History of I/O: Plugboard computers (ENIAC, <1946)

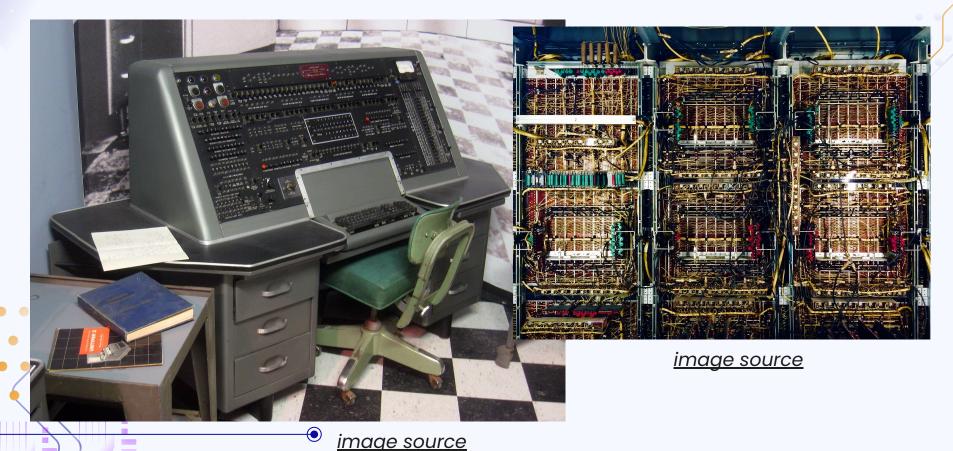

### History of I/O: UNIVAC 1 (1951)

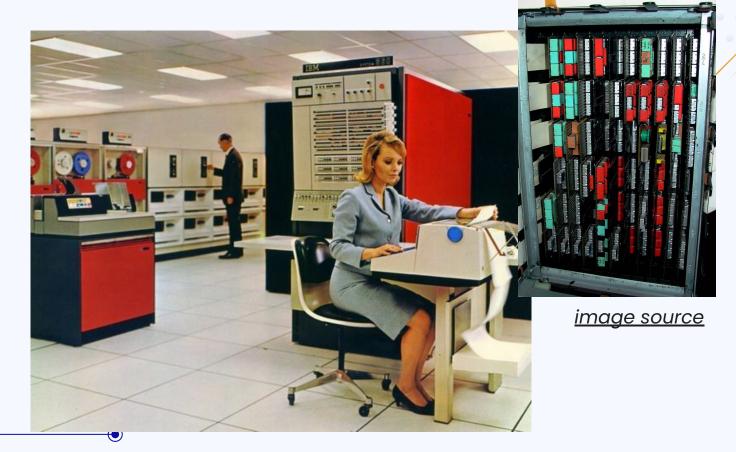

### History of I/O: IBM System/360 (>=1964)

image source

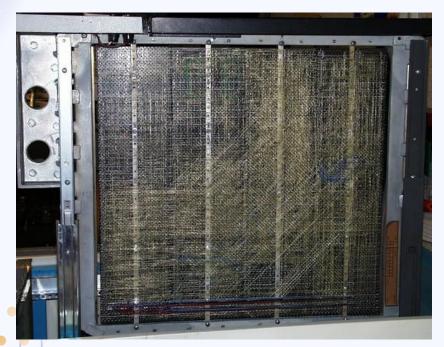

### History of I/0: PDP-8 (>=1965)

$\odot$

image source

image source

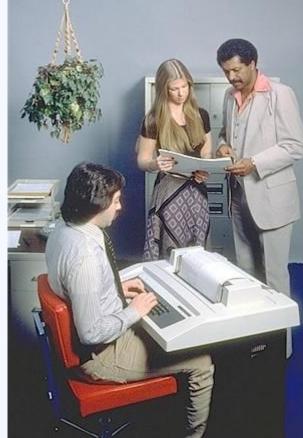

# VAX11: Successor to the PDP (1977)

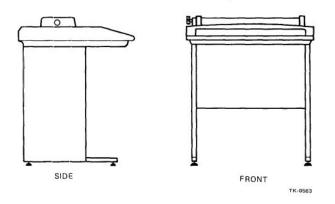

#### 5.2 LA36 TERMINAL

The LA36 DECwriter II is a medium-sized, low-cost, interactive data communications terminal (Figure 5-1). It is designed as an I/O device that is used in the VAX-11/780 system console subsystem and may be used as a remote communications terminal or a user terminal.

Figure 5-1 LA36 DECwriter II

source (VAX11 hardware user's guide)

<u>image source</u>

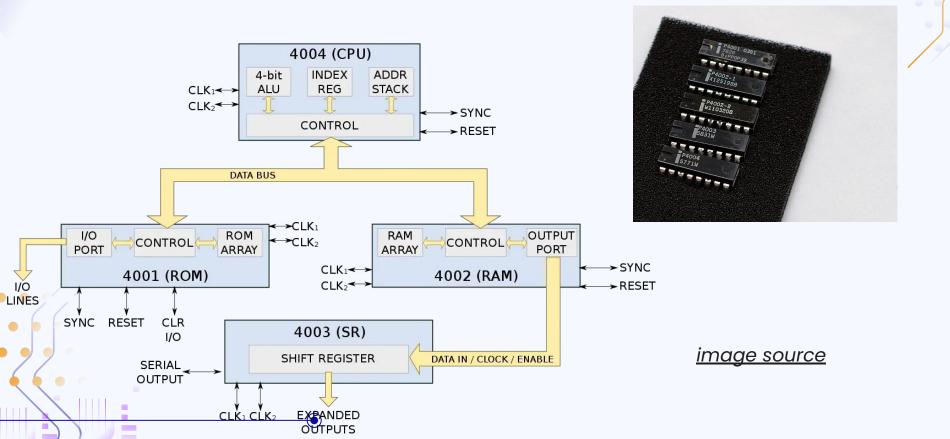

#### History of I/O: Intel 4004/MCS-4 (1971)

7

#### History of I/O: IBM PC (1981)

2

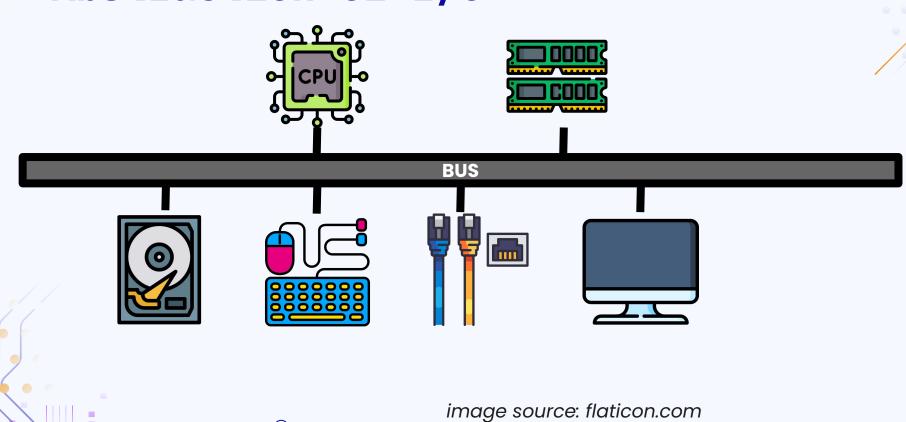

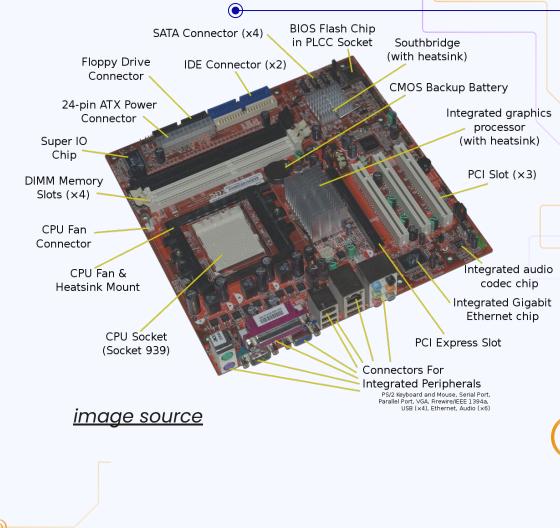

# **Motherboards**

Motherboard: printed circuit board (PCB) that holds computer components

Chipset: (usually on mobo) circuit that manages connection of CPU w/ memory and peripherals

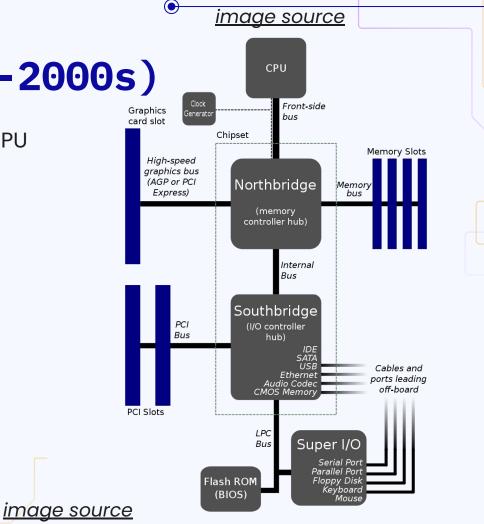

# Chipsets (1990s-2000s)

Northbridge: connects CPU, RAM, GPU Southbridge: slower, connects I/O

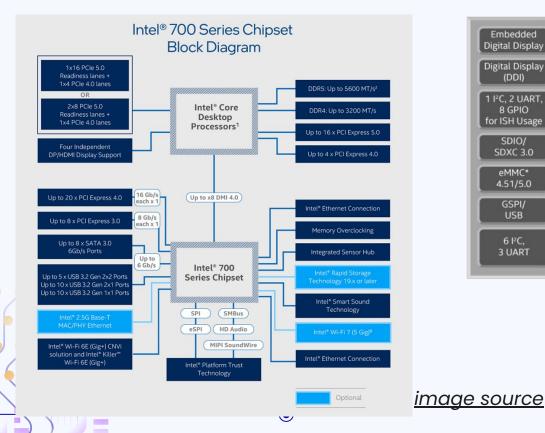

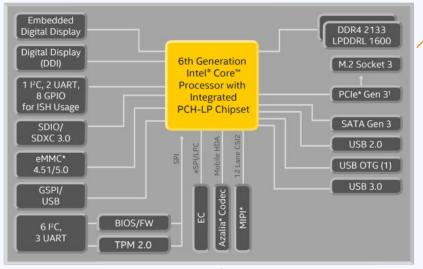

# **Evolution of chipsets (Intel)**

<sup>†</sup> Gen 3.0 available on premium PCH only. Gen 2.0 available on base PCH SKUs.

## **Buses**

There are many ways to transfer data

Different bus standards are used for different applications

SATA is used for storage (also NVME)

PCI/e is used for many things (GPU, sound, ethernet...)

SPI is used for serial embedded communication

We're not going to memorize these technologies – just know that there are different protocols for them

# ???

How does a CPU access an I/O bus? There's no lio or sio instruction in RISCV...

# Memory-mapped I/O

Memory-mapped I/O: hardware translation of some memory addresses to status and control registers of I/O devices

CPU writes/reads that address as usual, gets info about device Kernel-space (not user-space) addresses

Contrast with port-mapped I/O: special instructions to access I/O ports

x86 in and out instructions (x86 supports both port- and memory-mapped I/O; see chapter 19 of the <u>Intel 64 manual</u>)

#### Network Stress S

#### File Edit View Help

| System Summary       | Reso                 | ırce             | Device                                                          | Status       |  |

|----------------------|----------------------|------------------|-----------------------------------------------------------------|--------------|--|

| Hardware Resources   | OxFE                 | COOOO-OxFEDC7F.  | Motherboard resources                                           | OK           |  |

| - Conflicts/Sharing  | OxFE                 | DA0000-0xFEDA0   | Motherboard resources                                           | OK           |  |

| DMA                  | OxFE                 | DA1000-0xFEDA1   | Motherboard resources                                           | OK           |  |

| - Forced Hardware    | OxEO                 | 000000-0xEFFFFFF | Motherboard resources                                           | OK           |  |

| -1/0                 | OxFE                 | 020000-0xFED7FF. | . Motherboard resources                                         | OK           |  |

| IRQs                 | OxFE                 | 090000-0xFED93F. | . Motherboard resources                                         | OK           |  |

| Memory               | OxFE                 | 045000-0xFED8FF. | . Motherboard resources                                         | ОК           |  |

| Components           | 1000 P               |                  | Motherboard resources                                           | OK           |  |

| Multimedia           |                      |                  | - Intel(R) Serial IO I2C Host Controller - A0C5                 | OK           |  |

| CD-ROM               |                      |                  | Intel(R) Serial IO UART Host Controller - A0A8                  | OK           |  |

| -Sound Device        |                      |                  | Intel(R) USB 3.10 eXtensible Host Controller - 1.2.             |              |  |

| Display              |                      |                  | Intel(R) Wi-Fi 6 AX201 160MHz                                   | OK OK        |  |

| Infrared             |                      |                  | the second state was to be a first over the second state in the |              |  |

| Input                |                      |                  | Intel(R) USB 3.10 eXtensible Host Controller - 1.2.             |              |  |

| - Modem<br>⊞ Network |                      |                  | Intel(R) Serial IO I2C Host Controller - A0D8                   | OK           |  |

| Ports                |                      |                  | F Motherboard resources                                         | OK           |  |

|                      |                      |                  | F Motherboard resources                                         | OK           |  |

| Storage Printing     | 10000                |                  | Motherboard resources                                           | OK           |  |

| Problem Devices      |                      |                  | Motherboard resources                                           | OK           |  |

| USB                  |                      |                  | Motherboard resources                                           | OK           |  |

| Software Environment | OxFF                 | 00000-0xFFFFFFFF | Motherboard resources                                           | OK           |  |

| Software Environment | 0xFD                 | 000000-0xFD68FF. | Motherboard resources                                           | OK           |  |

|                      | 0xFD                 | 6B0000-0xFD6CFF. | Motherboard resources                                           | OK           |  |

|                      | 0xFD                 | 6F0000-0xFDFFFF  | Motherboard resources                                           | OK           |  |

|                      | 0xA0                 | 400000-0xA0403F. | Standard NVM Express Controller                                 | OK           |  |

|                      | 0xA0                 | 400000-0xA0403F. | PCI Express Root Complex                                        | OK           |  |

|                      | 0xA0                 | 400000-0xA0403F. | PCI Express Root Port                                           | OK           |  |

|                      | 0xA0                 | 404000-0xA0404   | Standard NVM Express Controller                                 | OK           |  |

|                      | OxFF                 | F8000-0xFFEFFFF  | Intel(R) Precise Touch and Stylus (Intel(R) PTS) - B.           | . OK         |  |

|                      | 0x11                 | 28000-0x112FFFF  | Intel(R) Platform Monitoring Technology Driver                  | OK           |  |

|                      |                      | 00-0xFFFFFF      | Intel(R) Iris(R) Xe Graphics                                    | OK           |  |

|                      |                      | 00-0xFFFFFFF     | Intel(R) Iris(R) Xe Graphics                                    | OK           |  |

|                      |                      |                  | F Intel(R) SPI (flash) Controller - A0A4                        | OK           |  |

|                      |                      |                  | . Intel(R) Serial IO GPIO Host Controller - INT34C5             | OK           |  |

|                      |                      |                  | Intel(R) Serial IO CDIO Last Controller INT34C5                 | OK           |  |

|                      | Find what:           |                  | Fin                                                             | d Close Find |  |

|                      | Search selected cate |                  | arch category names only                                        |              |  |

•

. .

•

-

-

. . . . . . .

– 🗆 X

# Bypassing CPU for memory access

Cumbersome idea: use processor to transfer data from user space to memory-mapped I/O space

Supervisor transfers pages from disk using 1k lw + sw instructions

**PCle**

endpoint

**PCle**

endpoint

Switcl

**Direct Memory Access** (DMA) transfers data to and from memory without going through the CPU, using the controller of the I/O device

PCIe uses an optimized version of DMA that involves bus arbitration

image source

CPU

**Root complex**

**PCle**

endpoint

Legacy

endpoint

Memory

PCle

bridae to

PCI/PCI-X

# $\mathbf{O}$

# ???

How should an I/O event (such as a keyboard key press) be detected and handled by the computer?

# Polling

Manually check the status of I/O device periodically

Pros:

Check message app over and over for your crush to text you

# Interrupts

Disrupt CPU execution when an I/O operation happens

Pros:

Get push notification that your crush has texted you

# **Exceptions vs Interrupts**

**Exception**: unscheduled event that disrupts execution (P&H chapter 4)

SW source: RISC-V ecall/ebreak instructions to invoke supervisor/debugger

HW source: divide by 0 or page fault

Interrupt: an exception that comes from outside the CPU

DMA I/O interrupt

Warning: terminology changes depending on textbook/context

What does the CPU hardware need to do when an exception happens?

# Handling exceptions

- Figure out if we need to stop immediately or finish current instruction Hardware exceptions: immediately (can't proceed after dividing by 0)

I/O interrupts: handle asynchronously (finish instruction)

- 2) Save processor state and provide exception info to supervisor

- 3) Switch control to supervisor

- 4) Go to PC of exception-handling routine

- 5) Handle exception

- 6) Switch back

# **RISC-V** exception registers

SEPC holds address of exception-causing instr

SCAUSE holds the cause

**STVAL** holds info about exception (e.g. fault-causing virtual address)

SIP holds pending status of potential interrupts

**STVEC** holds address of supervisor exception-handler

Alternative approach: vectored interrupts (arm)

| RISC-V shar v? | Table 12  |

|----------------|-----------|

| RISC-V spec v2 | Table 4.2 |

| Τ         | E di           | Descietion                     |

|-----------|----------------|--------------------------------|

| Interrupt | Exception Code | Description                    |

| 1         | 0              | Reserved                       |

| 1         | 1              | Supervisor software interrupt  |

| 1         | 2-4            | Reserved                       |

| 1         | 5              | Supervisor timer interrupt     |

| 1         | 6-8            | Reserved                       |

| 1         | 9              | Supervisor external interrupt  |

| 1         | 10 - 15        | Reserved                       |

| 1         | $\geq 16$      | Designated for platform use    |

| 0         | 0              | Instruction address misaligned |

| 0         | 1              | Instruction access fault       |

| 0         | 2              | Illegal instruction            |

| 0         | 3              | Breakpoint                     |

| 0         | 4              | Load address misaligned        |

| 0         | 5              | Load access fault              |

| 0         | 6              | Store/AMO address misaligned   |

| 0         | 7              | Store/AMO access fault         |

| 0         | 8              | Environment call from U-mode   |

| 0         | 9              | Environment call from S-mode   |

| 0         | 10-11          | Reserved                       |

| 0         | 12             | Instruction page fault         |

| 0         | 13             | Load page fault                |

| 0         | 14             | Reserved                       |

| 0         | 15             | Store/AMO page fault           |

| 0         | 16 - 23        | Reserved                       |

| 0         | 24-31          | Designated for custom use      |

| 0         | 32-47          | Reserved                       |

| 0         | 48-63          | Designated for custom use      |

| 0         | >64            | Reserved                       |

# Handling exceptions

- Figure out if we need to stop immediately or finish current instruction Hardware exceptions: immediately (can't proceed after dividing by 0)

I/O interrupts: handle asynchronously (finish instruction) SIP

- 2) Save processor state and provide exception info to supervisor **SCAUSE, STVAL, SEPC**

- 3) Switch control to supervisor

- 4) Go to PC of exception-handling routine **STVEC**

- 5) Handle exception (uses info stored in SCAUSE, STVAL)

- 6) Switch back SRET instruction (uses info stored in SEPC)